# Reconfigurable Digital multiple beam forming with planar phased array RADAR on FPGA

<sup>1</sup>N.Pratibha, <sup>2</sup>Mrs.D. Kavitha, <sup>3</sup>Mrs.Surya mukhi

<sup>1</sup>N.Pratibha, M.tech(VLSI)& ASTRA, Bandlaguda,hyd. <sup>2</sup>Mrs D. Kavitha, M.tech(VLSI)&Assitant professor in ASTRA, Bandlaguda,hyd. <sup>3</sup>Mrs.Surya mukhi, M.tech(VLSI)& Assitant professor in ASTRA, Bandlaguda,hyd.

Abstract: Beam forming is a signal processing technique used in antenna arrays for directional signal transmission or reception. Phased array radar is very important in modern radar development, and multiple digital beams forming technology is the most significant technology in phased array radar. Digital multiple beam forming on each antenna element about large phased array radar is impossible in processor based digital processing units, because it needs simultaneous processing many A/D channels. In this project we resolve this problem by using a multi array based beam forming technique with multiplexed signal processing unit on FPGA. The conventional technique of completely duplicated hardware and also dynamic reconfiguration does not yield the real time parallel beam processing. The proposed technique employs multiplexed signal processing unit which is time shared for various beam formers. This technique provides simultaneous beams without any compromise on functionality. The scope of the work includes the VHDL modeling of 16 element phased array antenna system and RTL implementation of complex NCO, digital mixer, low pass filter, multiplexers, demultiplexers, ROM for coefficient storage and Multiplier unit. The VHDL simulation of all these blocks shall demonstrate the beam formation for multiple beams. Simulated antenna outputs are used to test the developed beam former. The design is functionally verified by simulating the code in ModelSim from Mentor Graphics. The FPGA synthesis is done using Xilinx ISE tool. The synthesis results of ISE are analyzed for timing and area. The hardware output i.e FPGA output shows on Chipscope pro analyzer.

## I. Introduction

of antennas in A phased array radar is an array which the relative phases of the respective signals feeding the antennas are varied in such a way that the effective radiation pattern of the array is reinforced in a desired direction and suppressed in undesired directions. An antenna array is a group of multiple active antennas coupled to a common source or load to produce a directive radiation pattern. Usually, the spatial relationship of the individual antennas also contributes to the directivity of the antenna array. Use of the term "active antennas" is intended to describe elements whose energy output is modified due to the presence of a source of energy in the element (other than the mere signal energy which passes through the circuit) or an element in which the energy output from a source of energy is controlled by the signal input. One common application of this is with a standard multiband television antenna, which has multiple elements coupled together.

Phased array transmission was originally developed in 1905 by Nobel Laureate Karl Ferdinand Braun who demonstrated enhanced transmission of radio waves in one direction. During World War II, Nobel Laureate Luis Alvarez used phased array transmission in a rapidly-steer able radar system for "ground-controlled approach", a system to aid in the landing of aero planes in Britain. At the same time GEMA in Germany built the PESA Mammut. It was later adapted for radio astronomy leading to Nobel Prizes for Physics for Antony Hewish and Martin Ryle after several large phased arrays were developed at the University of Cambridge. The design is also used in radar, and is generalized in interferometric radio antennas. In 2007 DARPA researchers announced a 16 element phased array integrated with all necessary circuits to send at 30–50 GHz on a single silicon chip for military purposes. The relative amplitudes of constructive and destructive interference effects among the signals radiated by the individual antennas determine the effective radiation pattern of the array. A phased array may be used to point a fixed radiation pattern, or to scan rapidly in azimuth or elevation. Simultaneous electrical scanning in both azimuth and elevation was first demonstrated in a phased array antenna at Hughes Aircraft Company, Culver City, CA, in 1957 "When phased arrays are used in sonar, it is called beam forming".

The phased array is used for instance in optical communication as a wavelength-selective splitter.

## A. Naval usage:

Phased array radar systems are also used by warships of many navies. Because of the rapidity with which the beam can be steered, phased array radars allow a warship to use one radar system for surface

detection and tracking (finding ships), air detection and tracking (finding aircraft and missiles) and missile uplink capabilities. Prior to using these systems, each surface-to-air missile in flight required dedicated firecontrol radar, which meant that ships could only engage a small number of simultaneous targets. Phased array systems can be used to control missiles during the mid-course phase of the missile's flight. During the terminal portion of the flight, continuous-wave fire control directors provide the final guidance to the target. Because the radar beam is electronically steered, phased array systems can direct radar beams fast enough to maintain a fire control quality track on many targets simultaneously while also controlling several in-flight missiles. The AN/SPY-1 phased array radar, part of the Aegis combat system deployed on modern U.S. cruisers and destroyers, "is able to perform search, track and missile guidance functions simultaneously with a capability of over 100 targets." Likewise, the Thales Herakles phased array multi-function radar onboard the Formidable class frigates of the Republic of Singapore Navy has a track capacity of 200 targets and is able to achieve automatic target detection, confirmation and track initiation in a single scan, while simultaneously providing mid-course guidance updates to the MBDA Aster missiles launched from the ship.<sup>[6]</sup> The German Navy and the Dutch Navy have developed the Active Phased Array Radar System (APAR).

Recently, phased array antennas have been included in RFID systems in order to significantly boost the reading capability of passive UHF tags passing from 30 feet to 600 feet. A phased array of acoustic transducers, denominated Airborne Ultrasound Tactile Display (AUTD), was developed at the University of Tokyo's Shinoda Lab to induce tactile feedback. This system was also demonstrated to enable a user to interactively manipulate virtual holographic objects.

### **B.**Types of phased radars (Types of Beam Forming):

There are two main different types of phased arrays, also called" beam formers".

- 1. Time domain beam formers

- 2. Frequency domain beam formers.

A time domain beam former works, as the name says, by doing time-based operations. The basic operation is called "delay and sum". It delays the incoming signal from each array element by a certain amount of time, and then adds them together. Sometimes a multiplication with a window across the array is done to increase the main lobe/side lobe ratio, and to insert zeroes in the characteristic.

There are two different types of frequency domain beam formers.

1. The first type separates the different frequency components that are present in the received signal into different frequency bins (using either an FFT or a filter bank). When different delay and sum beam formers are applied to each frequency bin, it is possible to point the main lobe to different directions for different frequencies. This can be an advantage for communication links.

2. The other type of frequency domain beam formers makes use of so called "Spatial Frequency". This means that an FFT is taken across the different array elements, not in time. The output of the N point FFT is N channels, which are evenly divided in space. This approach makes a simple implementation of several beam formers at the same time possible, but this approach is not flexible, because the different directions are fixed.

## C.Digital Beam forming:

Beam forming is a signal processing technique which is used in" sensor arrays for directional signal transmission or reception". This is achieved by combining elements in the array in such a way that signals at particular angles experience constructive interference while others experience destructive interference. Beam forming can be used at both the transmitting and receiving ends in order to achieve spatial selectivity. The improvement compared with Omni directional reception/transmission is known as the receive/transmit gain (or loss).Digital Beam Forming (DBF) is a combination between "the antenna technology" and "the digital technology". Workers in Sonar and Radar systems first developed the early ideas of digital beam forming. This coupled with the development of aperture synthesis techniques in radio astronomy lead to the development of the modern dipolar arrays.

Digital beam forming is based on the conversion of the RF signal at each antenna elements into two streams of binary baseband signals representing" cos and sin channels". These two digital baseband signals can be used to recover both the amplitudes and phases of the signals received at each element of the array. The process of digital beam forming implies weighting by a complex weighting function and then adding together to form the desired output. The key to this technology is the accurate translation of the analog signal into the digital regime. Close matching of several receivers is not achieved in hardware, but rather by applying a calibration process. It is expected that more and more of receiver functions will be implemented using software. Eventually one would expect that the receiver would be built using software rather than hardware.

An antenna can be considered to be a device that converts spatio temporal signals into strictly temporal signals, there by making them available to a wide variety of signal processing techniques. From a conceptual point of view, its sampled outputs represent all of the data arriving at the antenna aperture. No information is

destroyed, at least not until the processing begins and any compromises that are made in the processing stages can be noted and estimates made of the divergence of the actual system from the ideal.

- Digital beam forming networks:

- 1. An element space beam former.

- 2. Beam space digital beam former.

An element-space beam forming, where the data signals from the array elements are directly multiplied by a set of weights to form the desired beam. Rather than directly weighting the outputs from the array elements, they can be first processed by a multiple-beam beam former to form a suite of orthogonal beams. The output of each beam can then be weighted and the result combined to produce a desired output. This process is often referred to as the beam-space beam forming.

Digital beam forming Receiver

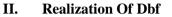

This is the main block diagram for digital beam forming consists of

- 3.1. RF Translator

- 3.2. ADC (Analog to Digital converter)

- 3.3 Digital Down-Counter

- 3.4. Multiplier

#### A. RF Translator:

Radio frequency (RF) is a rate of oscillation in the range of about 3 kHz to 300 GHz, which corresponds to the frequency of radio waves, and the alternating currents which carry radio signals. RF usually refers to electrical rather than mechanical oscillations, although mechanical RF systems do exist (see mechanical filter and RF MEMS).

In order to receive radio signals an antenna must be used. However, since the antenna will pick up thousands of radio signals at a time, a radio tuner is necessary to tune in to a particular frequency (or frequency range). This is typically done via a resonator - in its simplest form, a circuit with a capacitor and an inductor forming a tuned circuit. The resonator amplifies oscillations within a particular frequency band, while reducing oscillations at other frequencies outside the band.

#### **B.ADC** (Analog to Digital converter):

#### **C.Analog input interface (ADC):**

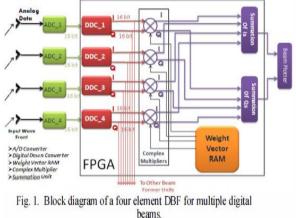

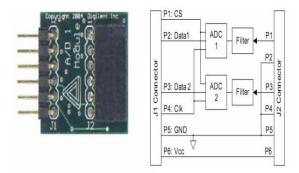

FPGAs are well suited for serial Analog to Digital (A/D) converters. This is mainly because serial interface consumes less communication lines while the FPGA is fast enough to accommodate the high speed serial data. The ADCS7476MSPS is a high speed, low power, 12-bit A/D converter. A/D converter is a high speed serial interface that interfaces easily to FPGAs. The A/D interface adapter (AD1\_PMOD) is implemented within the FPGA. Inside the FPGA, this adapter facilitates parallel data acquisition. Sampling is initiated at the rising edge of a clock applied at the line sample. The timing diagram of the communication protocol obtained with Modelsim is illustrated in shown Figure.

Figure 3.2 ADC connection diagrams

Figure 3.3 ADCS7476 Serial Interface Timing Diagram

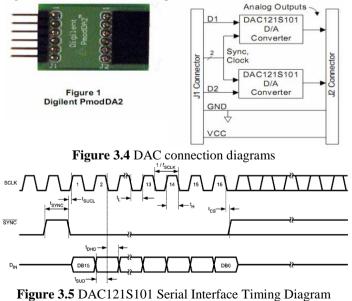

## C.Analog output Interface (DAC):

The DAC121S101 is a dual, 12-bit voltage out Digital to Analog (D/A) converter. This device uses a versatile 6-wire serial interface that operates at a clock up to 20 MHz. The serial input register is 16 bits wide; 12 bits act as data bits for the D/A converter, It is interfaced to an FPGA. The D/A interface adapter (DAC\_toplevel), which is implemented within the FPGA, facilitates parallel data input for the dual D/A converters. The timing diagram of the communication protocol is illustrated in Modelsim results.

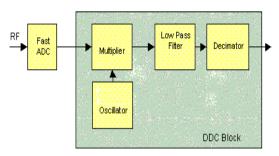

### **D**.Digital Down-Counter:

The Digital Down-Counter consists of sub modules of 3.3.1. Fast ADC 3.3.2. Oscillator (NCO)

3.3.3 Multiplier

3.3.4. Low Pass Filter

3.3.5. Decimator

Fig.3.6 Digital down Counter

The principle of Digital Down-Counter which is taking the input from RF Translator that is given to the input of Fast ADC .The output of Fast ADC block which is given to the DDC block. The DDC (Digital Down-Counter) consists of NCO (Numerically Controlled Oscillator), Multiplier, low pass

filter and Decimator.

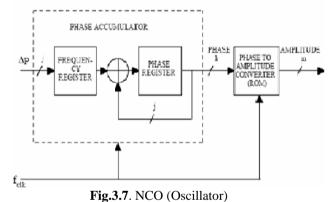

E.Oscillator (NCO):

The NCO main purpose is to generation the carrier signals (cosine). The main advantage is ROM based techniques will be used for area optimization.

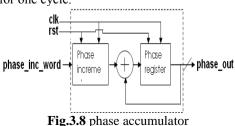

#### **Phase Accumulator Module:**

The phase accumulator consists of phase increment register, adder and phase register. The phase increment register stores the instantaneous phase increment values resulting from frequency modulation control block. This is fed to an 8 bit adder as one of its input. The other input for adder is phase register output. The phase register holds the instantaneous phase for each clock pulse. The accumulated phase also is represented by 8 bits, which limits the maximum phase by 11111111, and addition by 1 to maximum value causes the phase to become 00000000 this is expected and desired since the Look up Tables are programmed to consider 255 as highest phase value and phase increment by one results next cycle of waveform. Since 8 bits are used to represent the 0O to 360O the increment in digital phase value by one cause effective increment of 1.40625O (results by dividing 360O with 256 maximum possible combinations of 8 bits). This also implies that outputs can't have more that 256 samples for one cycle.

The output of phase accumulator when the phase increment value is 00000010000000000. It can be observed that the resulting phase value after each clock pulse is four added to the previous phase value. In the following figure initial phase is 0 and further with clock pulses resulting in 4, 8, 12, and 16 ... The output of phase accumulator is added with multiplier output. That output is given to NCO block.

All the blocks are connected with common clock and reset signals. The delta phase value decides the phase increment for each clock pulse. Hence decides the resulting signal frequency. The Frequency modulating instantaneous value is added to the delta phase value which causes instantaneous change in frequency. Due to the digital nature of the modulator only at each clock tick the modulating signal value shall affect the resulting frequency. If the modulating signal is analog then an Analog Digital converter must be used to digitize the modulating signal which can be used in NCO. The phase accumulator produces accumulated phase value for each clock pulse. In case if the DDS is used for phase modulation then instantaneous phase modulating signal value is added to the phase output of phase accumulator. This resulting phase value is given to the four Look Up Tables. Each Look Up Table is configured to produce a specific waveform. The logic used to generate the Look Up Tables is discussed in the further sections. The outputs of four Look Up Tables are given to the input lines a 4 to 1 Multiplexer. This multiplexer connects one of the inputs to the output depending on the select lines. The output of Multiplexer consists the 8 amplitude bits which is the final output in case required modulation schemes are FM or PM. In case of Amplitude modulation, the output of Multiplexer is multiplied with instantaneous modulating signal. In three modulation schemes if modulating signal is analog in nature then an appropriate Analog to Digital converter is required to convert into 8 bit digital output. the basic blocks in NCO can be identified as PIPO registers, adders, Look Up Tables and other combinational circuits. The following sections presents the implementation details and results obtained for all these blocks. The ModelSim tool from Mentor Graphics is used, for simulation and functional verification of NCO.VHDL has been used as design entry method for all these blocks. Xilinx ISE (Integrated Software Environment) XST (Xilinx Synthesis Tool) is used as a synthesis tool to implement the design on Spartan-3E FPGA. Chipscope pro is used for analyzing the implemented design.

### **1 PIPO n bit generic register:**

The Parallel in Parallel Out shift register cells are required in phase accumulator block to hold frequency and phase values. Synchronization is required between the phase increment register and phase register. This is achieved by connecting a common clock signal. Generic is used in VHDL implementation which allows to instantiate the PIPO component any bit size.

#### 2. N bit generic adder:

The N-bit generic adder is implemented in VHDL with simple ripple carry adder logic. The adder is tested with inputs A=011001, B=000101 and output observed is Z = 011110.

# F.Multiplier:

Here, The output generated by NCO as carrier signal which is multiplied with the ADC outputs. This output is given to next module as low pass filter.

#### G.Low Pass Filter:

A low-pass filter is an electronic filter that passes low frequency signals but attenuates (reduces the amplitude of) signals with frequencies higher than the cutoff frequency. The actual amount of attenuation for each frequency varies from filter to filter. It is sometimes called a high-cut filter, or treble cut filter when used in audio applications. A low-pass filter is the opposite of a high-pass filter. A band-pass filter is a combination of a low-pass and a high-pass.

#### **H.Decimator :**(Filtering & Decimation):

There are two main classes of DDC – wideband and narrowband, differentiated by their decimation ratios. As a rough guide, if the decimation ratio is less than 32, consider the DDC wideband; if 32 or more, the DDC is narrowband. The filtering we will perform is different for narrowband or wideband, so is tackled separately. However, the decimators can be treated identically for wideband or narrowband systems.

Note also that in some systems it may make sense to combine wideband and narrowband DDCs. For example, in a GSM system which uses 8 carriers, a wideband DDC could be used to shift the carriers down to a moderate frequency. This could be done using a simple oscillator - no complex components. 8 narrowband DDCs could then be used to select the individual carriers.

#### Filtering for Wideband DDCs:

With a wideband signal, we are typically reducing the sampling rate by a small amount, and the data output rate is large. Note that the output rate of a wideband DDC should be checked as part of our overall

system design. In some systems that data rate will be significant, and could saturate a DSP processor – if that is meant to be receiving it. The main challenge of a wideband receiver is getting enough processing to filter the signal. All the processing is performed at a fairly high rate, often 20-40MHz. Because of this, the filters tend to be very gate-intensive; a single wideband channel will typically consume more of an FPGA than several narrowband channels. Each design has different requirements. However, the following is a rough guide to implementing the filter. The filter is best implemented as an FIR, and in fact the best approach is to use a multirate FIR. This may sound complex, but in fact a multi-rate FIR is simply an efficient way of implementing large filters with decimation. Imagine we need to implement a large filter at a high sampling rate, before decimating the signal. However, suppose we split the filter. The first filter can perform enough filtering to allow us to perform some decimation. The second filter is now operating at a much reduced sampling rate. Typically by splitting the filter in this way we can reduce the number of taps in the filter, and reduce the sampling rate that some of these taps operate it. Both reduce the amount of FPGA resource we require to build the filter.

Immediately after this filter, decimate the signal by 2, and implement a larger filter. Again, the filter's bandwidth should match the DDC output bandwidth. This will improve the response of the first filter. One can afford to have more taps in this stage, as the sampling rate is lower.For higher decimation ratios (e.g. 8 and up), one can afford to use a third stage filter. This can have significantly more taps than the first two, as each multiplier here can implement at least 4x as many taps as in the first stage. Again, one will want to experiment with the layout of the filters to see what gives best performance.

### **Designing the Filters:**

There can be several tools by which the filter coefficients can be finalized for implementing the required FIR filters. In this project the MATLAB's filter design analysis tool (FDA) will be used for designing.

## III. Advantages

Digital beam forming allows several attractive features. Performances of communication systems can be improved while the digital beam forming is used. The main advantage to be gained from digital beam forming is greatly added flexibility without any attendant degradation in signal-to-noise ratio (SNR). A major advantage of digital beam forming lies in the fact that once the RF information is captured in the form of a digital stream, the way is clear for the application of a multitude of digital signal processing techniques and algorithms to the spatial domain data.

Digital beam forming is based on the conversion of the RF signal at each antenna elements into two streams of binary baseband signals representing I and Q channels. The digital baseband signals then represent the amplitudes and phases of signal received at each element of the array. The process of beam forming implies weighting these digital signals, thereby adjusting their amplitudes and phases such that when added together they form the desired beam

## IV. Conclusions

Digital beam forming allows several attractive features. Performances of communication systems can be improved while the digital beam forming is used. The main advantage to be gained from digital beam forming is greatly added flexibility without any attendant degradation in signal-to-noise ratio (SNR). The process of beam forming implies weighting these digital signals, thereby adjusting their amplitudes and phases such that when added together they form the desired beam. We used the Design and implementation of low-cost digital beam forming platform by using the FPGA (Spartan). The board supports for all digital blocks which can be implemented for Digital beam forming circuits have been tested to verify system operation.

In this project has explored the design and implementation of a low-cost digital beam forming platform. The board inputs and FPGA beam forming circuits have been tested to verify system operation. The proposed technique employs multiplexed signal processing unit which is time shared for various beam formers. This technique provides simultaneous beams without any compromise on functionality. The low cost of the system facilitates its easy integration into phased array radar systems.

## V. Future Enchancement

In this, by using a multi array based beam forming technique with multiplexed signal processing unit on FPGA. The conventional technique of completely duplicated hardware and also dynamic reconfiguration does not yield the real time parallel beam processing. The proposed technique employs multiplexed signal processing unit which is time shared for various beam formers. This technique provides simultaneous beams without any compromise on functionality.

Here we designed the digital beam forming by using the sampling frequency and the digital baseband signals then represent the amplitudes and phases of signal received at each element of the array. The process of beam forming implies weighting these digital signals.

In this project by using 16 antenna input signals we generated digital multiple beams with parallel array processing and we can implement more than 16 antenna input signals.

#### References

- [1]. J. G. McWhirter, "Recursive Least Squares minimization using a Systolic Array", Proc. SPIE 431, Real-Time Signal Processing VI, pp. 105-112, 1983.

- [2]. R. L. Walke, R. W. M. Smith and G. Lightboy, "Architectures for adaptive weight calculation on ASIC and FPGA", Proc. 33rd Asilomar Conference on Signals, Systems and Computers, pp 1375-1380, 1999.

- A. Farina, Antenna-Based Signal Processing Techniques for Radar systems, Artech House, 1991. [3].

- [4]. S. Haykin, Adaptive Filter Theory, 4th Edition, Pearson, ISBN 978-81-3 17-0869-9, pp 4-22, 20 1 1.

- [5]. Virtex-V Data Sheets and Application notes, Xilinx Inc.

- Virtex-VI Data Sheets and Application notes, Xilinx Inc. [6].

- N. Fourikis, Advanced Array Systems, applications and RF Technologies, Academic Press, San Diego, pp 1-8, pp 1 12- 122,2000. [7].

- [8]. P. S. Hall and S. 1. Vetterlien, "Integrated multiple beammicrostrip arrays", Microwave 1., V ol. 35, N o. I, 103, 1992.

- H. Steyskal and I. Rose, "Digital beamforming for radar system," Microwave 1., V ol. 32, 121, J an. 1989.

M. 1. Skolnik, Introduction to Radar Systems, Tata-McGraw Hill, 2004. [9].

- [10].

- e. A. Balanis, Antenna Theory Analysis and Design, JohnWiley & Sons, New York, 2004. [11].

- [12]. 1. Antonio Apolin'ario Jr., QRD-RLS Adaptive Filtering, IS\ ed., Springer Publications, pp 51-77, 2008.

- B. A. Shenoi, Digital Signal Processing and Filter Design, Wiley Interscience, 2006 [13].

- J. Bhasker, A VHDL Primer, P T R Prentice Hall, pp 4-106, 1999 [14].

- [15]. W. H. Wedon, "Phased array digital beamforming hardware development at applied radar ", IEEE international symposium on Phased array systems and technology, pp-854-859, 20 10.